Doctoral Dissertations and Master's Theses

Summer 8-2017

### A GPS Signal Generator Using a ROACH FPGA Board

Kurt L. Pedrosa Embry-Riddle Aeronautical University

Follow this and additional works at: https://commons.erau.edu/edt

Part of the Systems and Communications Commons

#### Scholarly Commons Citation

Pedrosa, Kurt L., "A GPS Signal Generator Using a ROACH FPGA Board" (2017). *Doctoral Dissertations and Master's Theses*. 373. https://commons.erau.edu/edt/373

This Thesis - Open Access is brought to you for free and open access by Scholarly Commons. It has been accepted for inclusion in Doctoral Dissertations and Master's Theses by an authorized administrator of Scholarly Commons. For more information, please contact commons@erau.edu.

### A GPS Signal Generator Using a ROACH FPGA Board

A Thesis submitted in partial fulfillment of the requirements for the award of the degree of

Master of Science in Electrical and Computer Engineering

> Submitted by Kurt L. Pedrosa

Under the guidance of Dr. William C. Barott

DEPARTMENT OF ELECTRICAL, COMPUTER, SOFTWARE, AND SYSTEMS ENGINEERING

RADAR & MICROWAVES LABORATORY Daytona Beach, Florida - USA

August 2017

### Committee Approval

#### "A GPS SIGNAL GENERATOR USING A ROACH FPGA BOARD" Kurt L. Pedrosa

This thesis is prepared under the direction of the candidate's thesis committee chairman, Dr. William C. Barott, Department of Electrical, Computer, Software, and Systems Engineering, and has been approved by members of his thesis committee. It is submitted to the Electrical, Computer, Software, and Systems Engineering Department in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering.

Dr. William C. Barott Committee Chairman

Digitally signed by Brian Butka Date: 2017.08.23 12:00:54 **Brian Butka** -04'00'

Dr. Brian Butka Committee Member

Dr. Richard Stansbury Committee Member

Dr. Tim Wilson Department Chair

Dr. Maj Mirmirani Dean of College of Engineering

Dr. Christopher Grant Vice Chancellor for Academics

241/2 2017 Date

8/24/2017

Date

8/25/17 Date

Embry-Riddle Aeronautical University

## Abstract

Master of Science in Electrical and Computer Engineering

#### A GPS Signal Generator Using a ROACH FPGA Board

by Kurt Pedrosa

Dr. William C. Barott, Dr. Richard Stansbury, Dr. Brian Butka Department of Electrical, Computer, Software, and Systems Engineering

A Global Positioning System (GPS) signal simulator is a valuable testing tool. It allows for testing of GPS receivers, systems, and anti-spoofing algorithms. With the increased popularity of software defined radios (SDRs) merging GPS signal simulators and SDRs is a natural choice. A detailed review of the construction of a GPS signal generator using the ROACH processing board is presented herein. The ROACH, developed by the Collaboration for Astronomy Signal Processing and Electronics Research (CASPER) team, is a processing board that can be configure to function as a SDR. In this research, the ROACH was transformed to function as a GPS signal generator able to transmit the C/A L1 civilian GPS signal. Maximum manipulation of the GPS signal was built-in to the firmware allowing the user to change the signal for different applications. Its modular architecture and ease of reproduction makes this GPS signal simulator design a viable research tool in the field of GPS anti-spoofing, GPS system fabrication, and as a great GPS educational tool. The GPS signal generator presented herein simulates the GPS C/A L1 signal at a frequency of 50.127 MHz. The generated signal contains no time delay or Doppler shift. A total of four independent GPS signals can be generated and transmitted as a single composite signal. The signal generator is capable of generating all of the current NAVSTAR defined PRN sequences allowing the simulation of any four satellite combination. It also uses the most up-to-date almanac data in the transmitted signal.

Future improvements to this GPS signal generator includes development of an up-converter to convert the transmitted signal frequency to the C/A L1 signal frequency of 1575.42 MHz, implementation of Doppler shift and time delay logic to the firmware, and software front end providing the user the ability to enter trajectory coordinates used to generate dynamic GPS signal along defined trajectory.

### Acknowledgements

As this stressful but extremely rewarding period comes to an end the time has come to give acknowledgments to those who cheered me on every step of the way. I would first like to thank my thesis advisor, Dr. William C. Barott at Embry-Riddle Aeronautical University. He has been a beacon of strength, a well of patience. He has guided me every step of the way and set me up for a bright professional future. He has made me a life long student excited about discovery, learning, and curiosity.

To the Electrical, Computer, Software, and System (ECSSE) department at Embry-Riddle Aeronautical University I extend my deepest appreciation. With special mention of Dr. Brian Butka and Dr. Richard Stansbury for their support on this thesis research. To Dr. Timothy Wilson and Professor Farahzad Behi for all of their help and patience. As my days end as a student in the Department the memories and growth gained will forever remain. My time spent there will forever be in my heart.

Most importantly I would like to acknowledge the three women of my life. My Grandmother, Reny De Lima Torres, who at 89 years old continues to be the biggest trouble maker in the family. To my Mother, Sheila Tecchio; Your perseverance, strength, and determination inspires me. The man I am today is because of her. To my Wife, Michelle Dos Anjos Pedrosa, who is my biggest cheerleader. She endured countless lonely days and nights while I finished my thesis. All I am is hers, who I became will be because of her.

# Contents

| Al            | bstra | act                       | ii    |

|---------------|-------|---------------------------|-------|

| Ac            | cknov | wledgements               | vi    |

| Co            | onter | nts                       | x     |

| Li            | st of | Figures                   | xv    |

| $\mathbf{Li}$ | st of | Tables                    | xvi   |

| Al            | bbrev | viations                  | xviii |

| 1             | Intr  | roduction                 | 1     |

|               | 1.1   | Motivation                | . 1   |

|               | 1.2   | Thesis Organization       | . 2   |

| <b>2</b>      | Bac   | kground and Theory        | 4     |

|               | 2.1   | Global Positioning System | . 4   |

|               | 2.2   | Orbital Description       | . 7   |

|   | 2.3 | Almai           | nac and Ephemeris                       | 10 |

|---|-----|-----------------|-----------------------------------------|----|

|   | 2.4 | GPS S           | Signal Characteristics                  | 12 |

|   |     | 2.4.1           | Binary Phase Shift Keying               | 16 |

|   |     |                 | 2.4.1.1 Direct Sequence Spread Spectrum | 17 |

|   |     | 2.4.2           | C/A Code                                | 19 |

|   |     | 2.4.3           | Message Signal Format                   | 24 |

|   | 2.5 | Augm            | entation Systems                        | 27 |

|   |     | 2.5.1           | Global Differential GPS                 | 28 |

|   |     | 2.5.2           | Wide Area Augmentation System           | 28 |

| 3 | Met | thodol          | ogy                                     | 31 |

|   | 3.1 | GPS S           | Signal Reproduction                     | 31 |

|   |     | 3.1.1           | ROACH FPGA                              | 32 |

|   |     | 3.1.2           | Firmware                                | 33 |

|   |     |                 | 3.1.2.1 Single Signal Model             | 35 |

|   |     |                 | 3.1.2.2 Multisignal Model               | 48 |

|   |     |                 | Ŭ                                       |    |

|   |     |                 | 3.1.2.3 Lessons Learned                 | 49 |

|   | 3.2 | Softwa          |                                         |    |

|   | 3.2 | Softwa<br>3.2.1 | 3.1.2.3 Lessons Learned                 | 50 |

|   |     | 3.2.3  | Supporting Functions                                                                               |

|---|-----|--------|----------------------------------------------------------------------------------------------------|

|   |     | 3.2.4  | Lessons Learned                                                                                    |

|   | 3.3 | GPS S  | oftware Decoder                                                                                    |

|   |     | 3.3.1  | Post-Processing                                                                                    |

|   |     | 3.3.2  | Decoder                                                                                            |

|   | 3.4 | Signal | Acquisition                                                                                        |

|   |     | 3.4.1  | Ettus N210 SRD                                                                                     |

|   |     |        | 3.4.1.1 WBX USRP Daughterboard                                                                     |

|   |     | 3.4.2  | GNU Radio Software                                                                                 |

|   |     |        | 3.4.2.1 Lessons Learned $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 75$ |

|   |     | 3.4.3  | GNSS-SDR Project                                                                                   |

|   |     |        | 3.4.3.1 Lessons Learned                                                                            |

| 4 | Res | ults   | 83                                                                                                 |

|   | 4.1 | Hardw  | are Setup                                                                                          |

|   | 4.2 | GPS S  | ignal Validation                                                                                   |

|   |     | 4.2.1  | PRN Signal Validation                                                                              |

|   |     | 4.2.2  | Test Vector Data Results                                                                           |

|   |     | 4.2.3  | Message Signal Validation                                                                          |

|   |     |        | 4.2.3.1 Lessons Learned                                                                            |

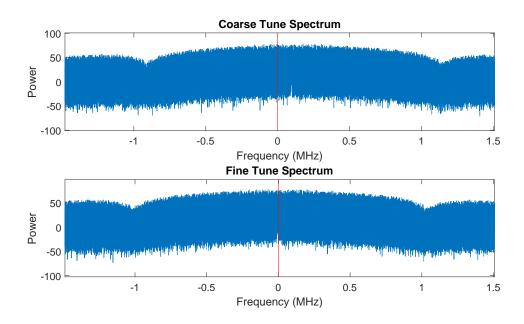

|   | 4.3                  | Ettus SDR Results     | 108 |

|---|----------------------|-----------------------|-----|

|   |                      | 4.3.1 Lessons Learned | 113 |

|   | 4.4                  | Decoder Results       | 114 |

| 5 | Res                  | search Conclusion     | 122 |

| 6 | $\operatorname{Fut}$ | ture Work             | 124 |

| R | efere                | ences                 | 128 |

# List of Figures

| 2.1  | GPS Constellation Map [6]                                                          | 5  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | GPS Control Segment Map [7]                                                        | 6  |

| 2.3  | Keplerian orbital elements                                                         | 9  |

| 2.4  | Different Almanac Formatting of Satellite with PRN 1 $\ldots \ldots$               | 11 |

| 2.5  | SPS and PPS signal structure                                                       | 15 |

| 2.6  | Generation of BPSK on a sinusoidal carrier frequency                               | 16 |

| 2.7  | BPSK modulation                                                                    | 17 |

| 2.8  | XOR multiplication of two signals                                                  | 18 |

| 2.9  | DSSS modulation [2] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 19 |

| 2.10 | C/A code generator design schema. $G_1$ register in green, $G_2$ register          |    |

|      | in red, and the <i>Bit Selector</i> in yellow                                      | 21 |

| 2.11 | Subframe structure, size, and direction of data flow from SV $\ . \ . \ .$         | 24 |

| 2.12 | Telemetry word format                                                              | 25 |

| 2.13 | Handover word format                                                               | 26 |

| 2.14 | Timing graph of the GPS message data                                               | 27 |

| 2.15 | WASS LPV Coverage [23]                                                                    | 29 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.1  | Diagram showing connection between the software and the firmware                          | 32 |

| 3.2  | Complete firmware flow diagram with markings identifying the sig-<br>nals of the four SVs | 35 |

| 3.3  | Block flow diagram of the single signal model highlighting the four subsystems            | 36 |

| 3.4  | PRN Clock subsystem showing clock divider logic and bit stream size                       | 38 |

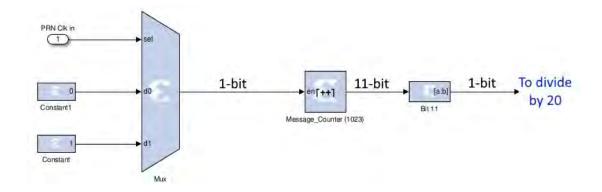

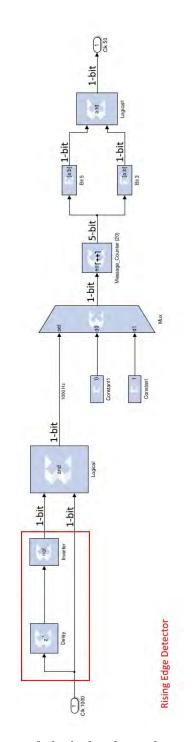

| 3.5  | First sequence of clock divider reducing a 1.023 MHz clock to 1000Hz                      | 39 |

| 3.6  | Second sequence of clock divider reducing a 1000 Hz clock to 50 Hz $$                     | 40 |

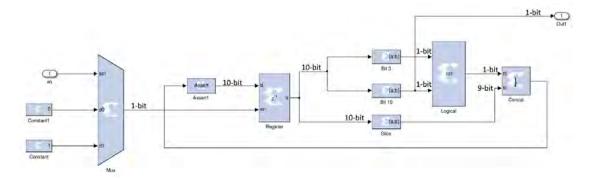

| 3.7  | G1 10-bit shift register logic                                                            | 41 |

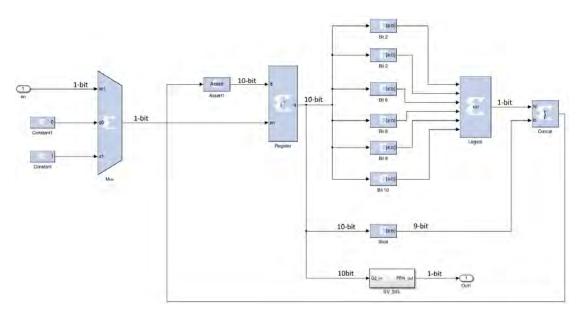

| 3.8  | G2 10-bit shift register logic                                                            | 42 |

| 3.9  | G2 register bit selector output logic                                                     | 42 |

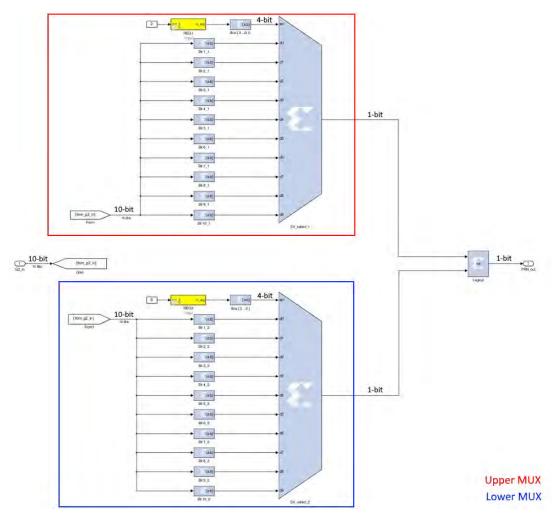

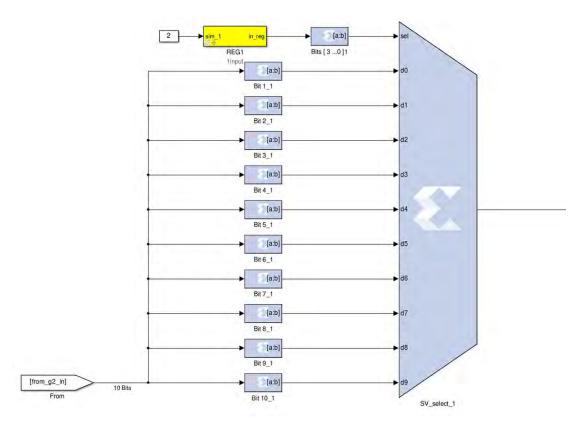

| 3.10 | Close-up of the G2 register bit selector upper MUX $\ldots \ldots$                        | 43 |

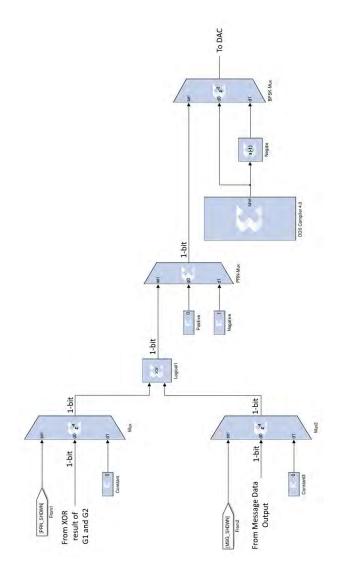

| 3.11 | Message Data subsystem block logic                                                        | 45 |

| 3.12 | PRN and Message bit modulation with the carrier signal $\ . \ . \ .$ .                    | 47 |

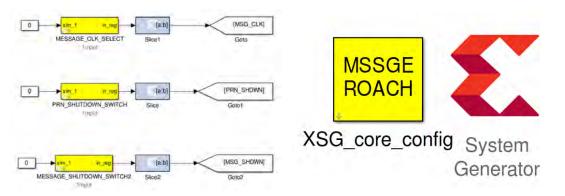

| 3.13 | Additional blocks used in the single signal model                                         | 48 |

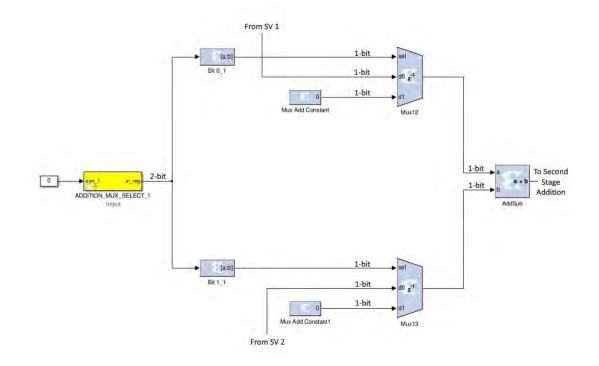

| 3.14 | Close-up view of the first stage addition logic                                           | 49 |

| 3.15 | High-level software flow diagram                                                          | 52 |

| 3.16 | High-level function flow diagram for the subframe generation process                      | 56 |

| 3.17 | Power density spectrum of both shifted signals                            | 64 |

|------|---------------------------------------------------------------------------|----|

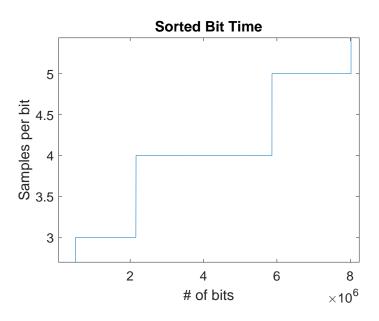

| 3.18 | Bit sample length at 4 MHz sample rate                                    | 65 |

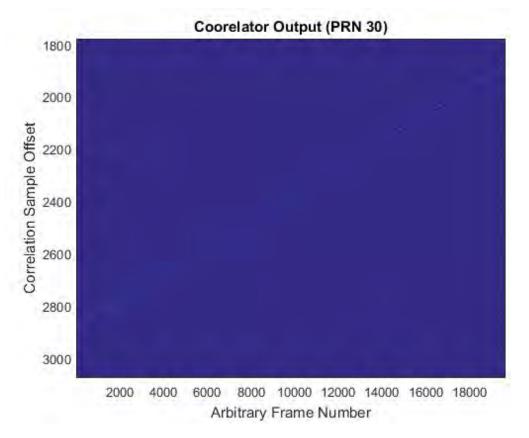

| 3.19 | Cross correlation result for PRN 30                                       | 66 |

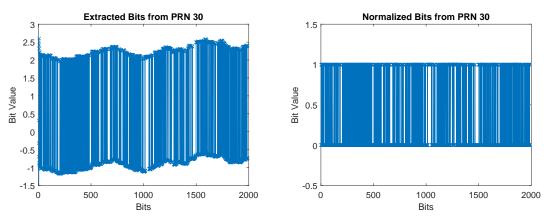

| 3.20 | Message data extracted from PRN 30 before and after normalization         | 67 |

| 3.21 | Message data bit stream from bits 580 to 780 before and after nor-        |    |

|      | malization                                                                | 68 |

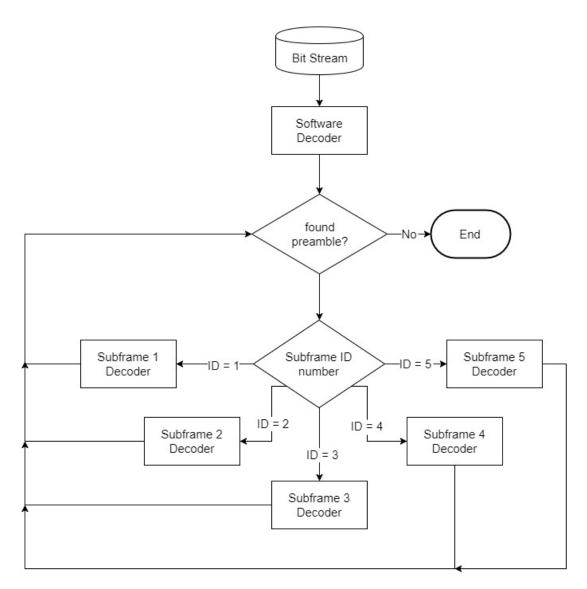

| 3.22 | High-level software decoder design                                        | 69 |

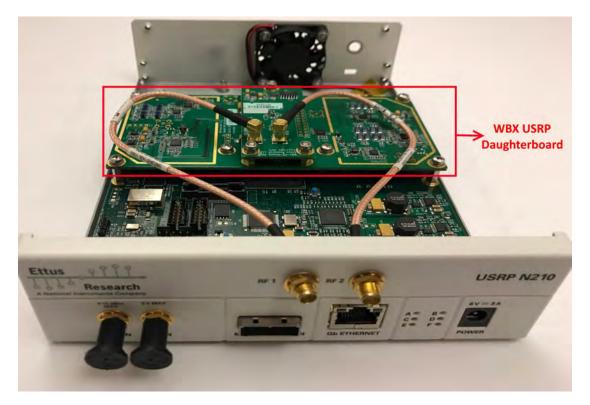

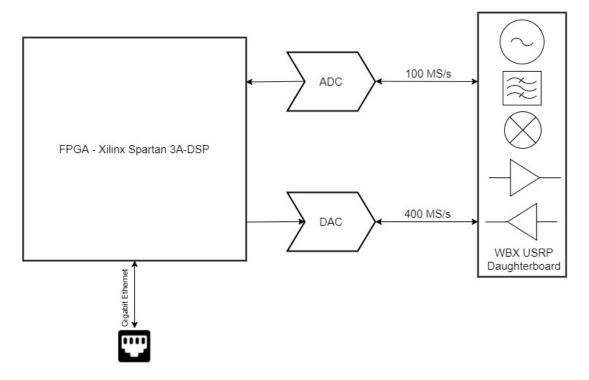

| 3.23 | Ettus N210 SDR showing the internal board and the WBX daugh-              |    |

|      | terboard                                                                  | 71 |

| 3.24 | High-level diagram of the Ettus N210 and WBX daughterboard                |    |

|      | connection                                                                | 73 |

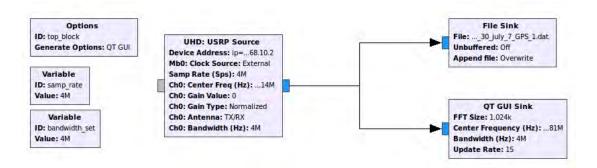

| 3.25 | Data recording and signal analysis GNU radio flow diagram $\ . \ . \ .$   | 76 |

| 3.26 | USRP Source block parameters                                              | 77 |

| 3.27 | General properties for the File Sink and QT GUI Sink blocks               | 78 |

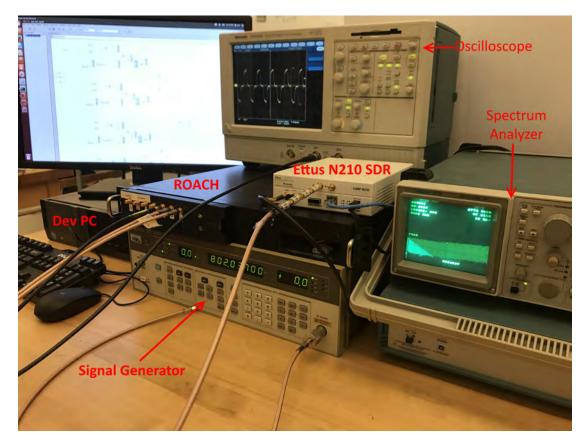

| 4.1  | Hardware setup                                                            | 84 |

| 4.2  | Signal Generator configurations and ROACH input/output ports              | 85 |

| 4.3  | Reference Clock connection between the Ettus and the signal gen-          |    |

|      | erator                                                                    | 86 |

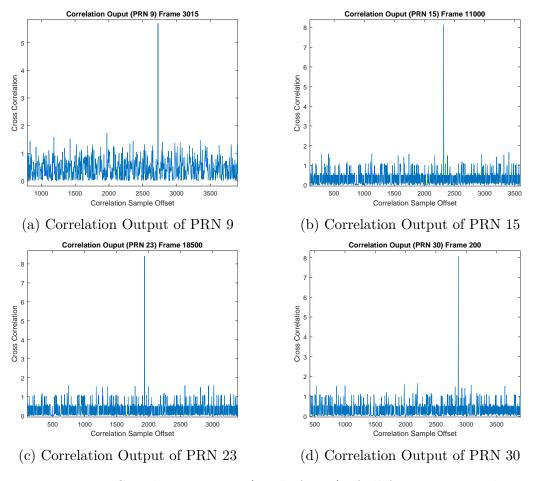

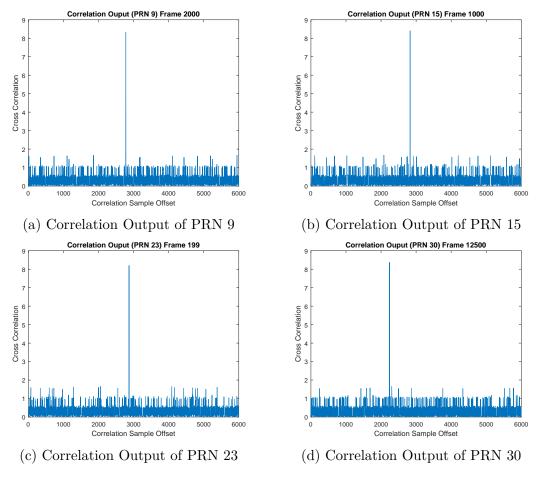

| 4.4  | Correlation output (single frame) of all four PRN signals $\ . \ . \ .$ . | 88 |

| 4.5  | Correlation output (all frames) of individually transmitted PRN           |    |

|      | signals                                                                   | 89 |

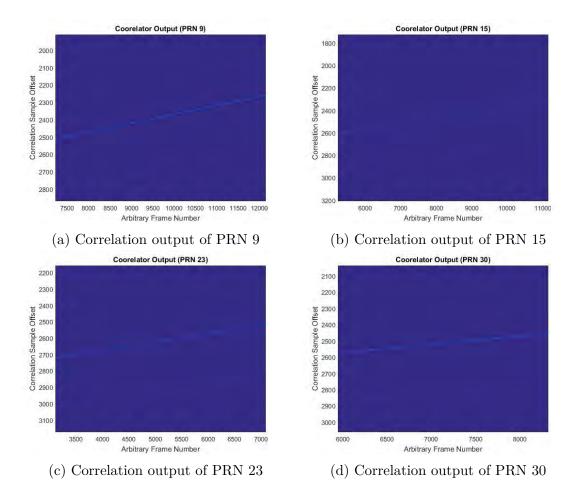

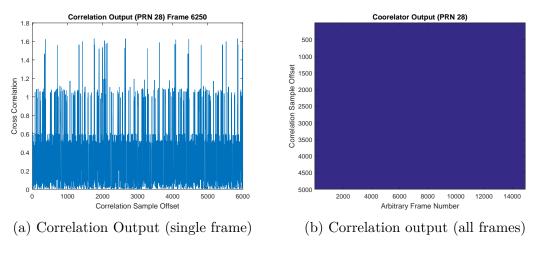

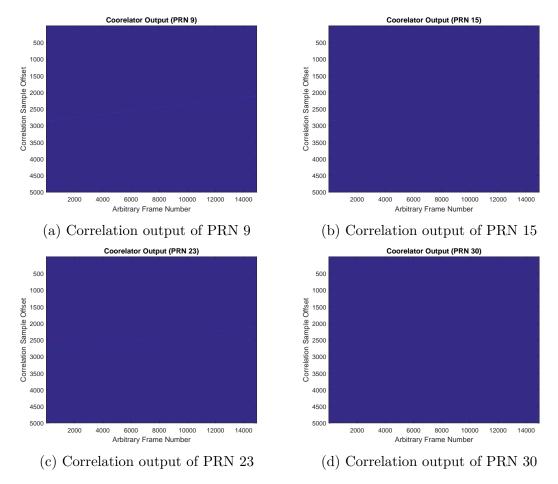

| 4.6 Low correlation output of PRN 28                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7 Correlation output (all frames) for composed transmitted signal $\ . \ . \ 91$                                                                                                  |

| 4.8 Correlation output (single frame) for composit signal 92                                                                                                                        |

| 4.9 Power spectrum of PRN signal                                                                                                                                                    |

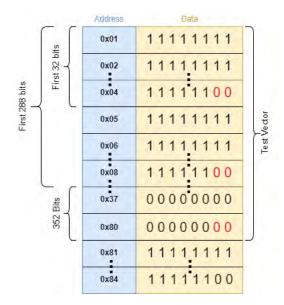

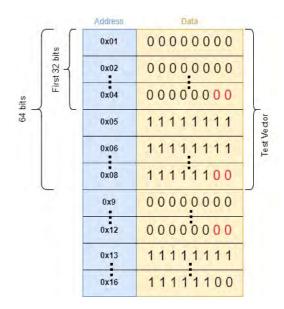

| 4.10 Diagram representing test vector data 1 stored in BRAM 95                                                                                                                      |

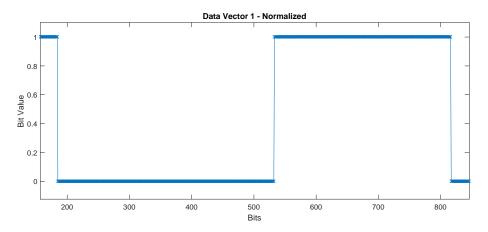

| 4.11 Normalized bit stream test vector 1 data received                                                                                                                              |

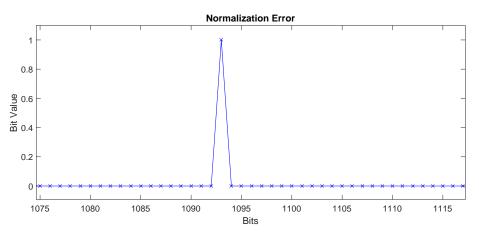

| 4.12 Bit normalization error                                                                                                                                                        |

| 4.13 Diagram representing test vector data 2 stored in BRAM 97                                                                                                                      |

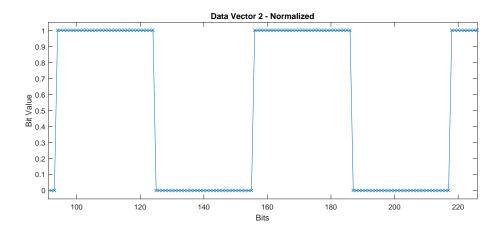

| 4.14 Normalized bit stream test vector 2 data received                                                                                                                              |

| 4.15 Diagram representing test vector data 3 stored in BRAM 98                                                                                                                      |

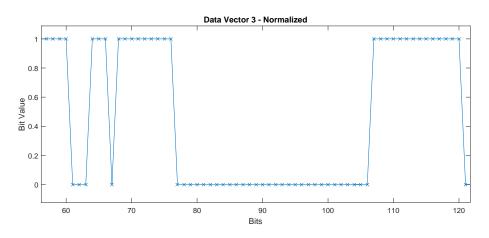

| 4.16 Normalized bit stream test vector 3 data received                                                                                                                              |

| 4.17 Diagram representing test vector data 4 stored in BRAM 99                                                                                                                      |

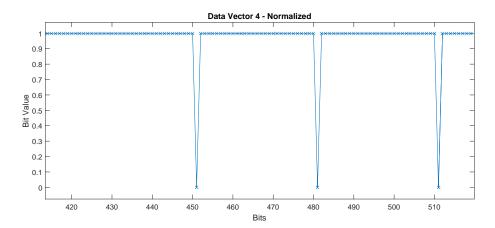

| 4.18 Normalized bit stream test vector 4 data received                                                                                                                              |

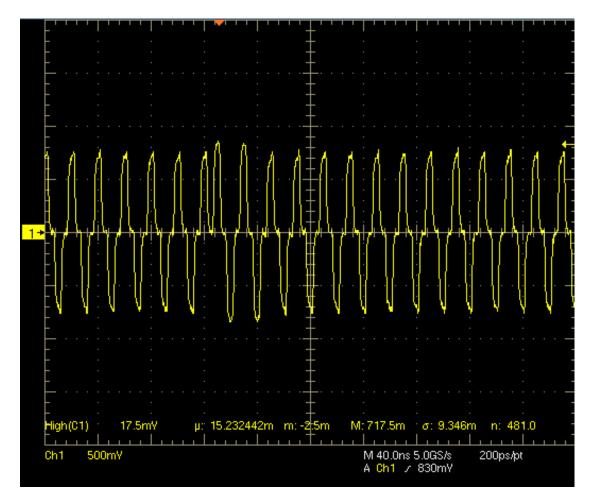

| 4.19 Message signal bit change at 40 ns                                                                                                                                             |

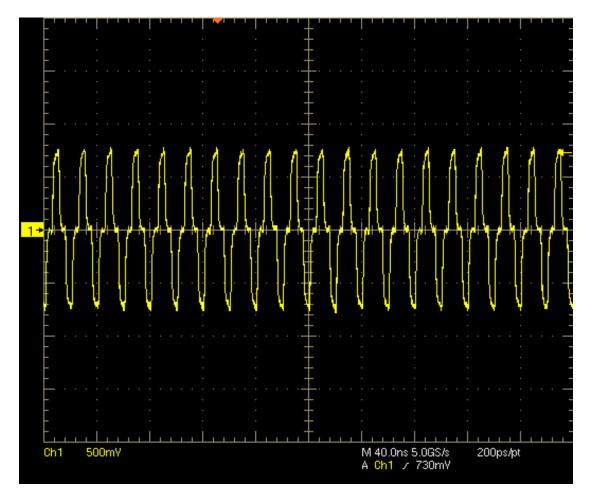

| 4.20 Visual inspection of message signal with no bit change at 40 ns 102                                                                                                            |

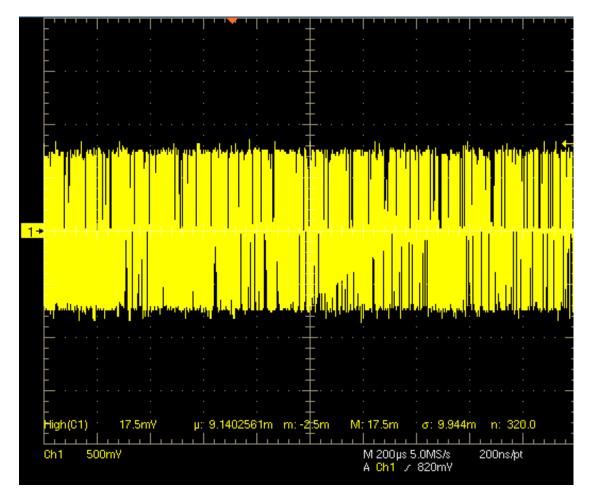

| 4.21 Message signal showing multiple bit changes at 200 $\mu$ s $\dots \dots \dots$ |

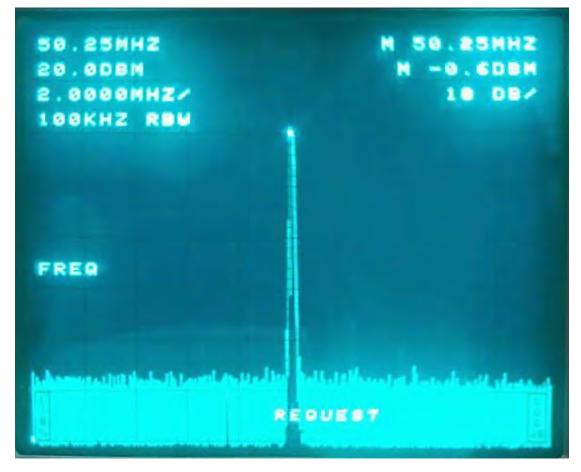

| 4.22 Power spectrum of the message signal centered at 50.127 MHz $$ 104                                                                                                             |

| 4.23 Sum of four message signals resulting in amplitude change $\ldots \ldots 105$                                                                                                  |

| 4.24 Message clock error showing burst of data every 10 ms $\ldots \ldots \ldots 107$                                                                                               |

| 4.25 Message clock error showing rapid change of bits                                                                                                                               |

| 4.26 | Connection between the ROACH and the Ettus N210 109                             |

|------|---------------------------------------------------------------------------------|

| 4.27 | Failed acquisition results from GNSS-SDR software                               |

| 4.28 | Partially successful acquisition results from GNSS-SDR software $\ . \ . \ 112$ |

| 4.29 | Subframe 4 decoded data                                                         |

| 4.30 | Subframe 4 data format as defined by NAVSTAR specifications 116                 |

| 4.31 | Subframe 5 decoded data                                                         |

| 4.32 | Subframe 5 data format as defined by NAVSTAR specifications $~$ 117             |

| 4.33 | Subframe 1 decoded data                                                         |

| 4.34 | Subframe 1 data format as defined by NAVSTAR specifications 118                 |

| 4.35 | Subframe 2 decoded data                                                         |

| 4.36 | Subframe 3 decoded data                                                         |

# List of Tables

| 2.1 | Ephemeris data definitions                                         |

|-----|--------------------------------------------------------------------|

| 2.2 | Truth table of the XOR 18                                          |

| 2.3 | C/A code bit assignment and first 10-chip sequence $\hdots$        |

| 3.1 | Summary of the various data contained in subframe 4 and 5 $\ .$ 57 |

| 4.1 | Almanac parameters with scale factors and number of bits 115       |

| 4.2 | Almanac data for SV 16 generated on July 6, 2017                   |

# Abbreviations

| ADC    | Analog to Digital Converter                |

|--------|--------------------------------------------|

| CASPER | Collaboration for Astronomy Signal         |

|        | Processing and Electronics Research        |

| C/A    | Coarse Acquisition Code                    |

| CTTC   | Centre Tecnològic de Telecomunicacions de  |

| 0110   | Cataluny                                   |

| BPSK   | Binary Phase Shift Keying                  |

| BRAM   | Block Random Access Memory                 |

| DAC    | Digital to Analog Converter                |

| DGPS   | Differential Global Positioning System     |

| DOD    | Department of Defense                      |

| DOT    | Department of Transportation               |

| DSSS   | Direct Sequence Spread Spectrum            |

| DTV    | Digital Television                         |

| FAA    | Federal Aviation Administration            |

| FPGA   | Field Programmable Gate Array              |

| GPS    | Global Positioning System                  |

| GNSS   | Global Navigation Satellite System         |

| GRC    | GNU Radio Companion                        |

| GUI    | Graphical User Interface                   |

| HDL    | Hardware Discriptive Language              |

| HOW    | Handover Word                              |

| ILS    | Instrument Landing System                  |

| IMU    | Inertial Measuring Unit                    |

| IP     | Internet Protocol                          |

| ISF    | Integrity Status Flag                      |

| LAN    | Local Area Network                         |

| LO     | Local Oscillator                           |

| LSB    | Least Significant Bit                      |

| LUT    | LookUp Tables                              |

| MEO    | Medium Earth Orbit                         |

| MUX    | Multiplexer                                |

| MSB    | Most Significant Bit                       |

| NASA   | National Aeronautics and Space             |

|        | Administration                             |

| NDGPS  | Nationwide Differential Global Positioning |

|        | System                                     |

| NMEA   | National Marine Electronics Association    |

| NUDET  | Nuclear Detonations                        |

| PC     | Personal Computer                          |

| PPS    | Precise Position Service                   |

|        |                                            |

| PRN            | $\mathbf{P}$ seudo $\mathbf{R}$ andom $\mathbf{N}$ oise |

|----------------|---------------------------------------------------------|

| PVT            | Position, Velocity, and Time                            |

| P(Y)           | Precision code                                          |

| RF             | Radio Frequency                                         |

| RINEX          | Receiver Independent Exchange Format                    |

| ROACH          | Reconfigurable Open Architecture                        |

|                | Computing Hardware                                      |

| SDR            | Software Defined Rardio                                 |

| SPS            | Standard Position Service                               |

| $\mathbf{SV}$  | ${f S}$ atellite ${f V}$ ehicle                         |

| SIS            | Signal-in-space                                         |

| TCP            | Transmission Control Protocol                           |

| $\mathbf{TLM}$ | Telemetry                                               |

| TOW            | Time of the Week                                        |

| UHF            | Ultra High Frequency                                    |

| UTC            | Coordinated Universal Time                              |

| USCG           | United States Coast Guard                               |

| USNDS          | United States Nuclear Detonation Detection              |

|                | System                                                  |

| VOR            | Very High Frequency Omnidirectional Range               |

| WAAS           | Wide Area Augmentation System                           |

| WMS            | Wide Area Augmentation System Master                    |

|                | Station                                                 |

| WRS            | Wide Area Augmentation System Reference                 |

|                | Station                                                 |

## Chapter 1

## Introduction

This chapter discusses the motivations that led to the work of this thesis research on GPS (Global Positioning System) signal simulation. It further presents an outline of this thesis document.

### 1.1 Motivation

A GPS signal generator is a valuable educational, research, and development tool. As a research and development tool it can be used to test new anti-spoofing algorithms, new GPS navigation systems, GPS dependent systems, and many others. As an educational tool it can be used to teach many subjects including the GPS signal structure, provide hands-on experience with signal transmission and acquisition, and provide live demonstration of signal processing applications. GPS signal generators can cost upwards of \$10,000, a price out of range for many research laboratories, universities, and enthusiasts. Naturally a demand exists for an inexpensive, modular system capable of generating a GPS signals for a wide range of applications.

GPS is the primary form of air, sea, and ground navigation used across all industries and virtually every part of the world. Problems like spoofing, signal multipath, and interference must be analyzed. A well-designed GPS signal simulator with a modular architecture fulfills not only nearly every research area but it can also be used as an educational tool.

To assist with GPS signal research and to promote education in this area were not the only motivators for this thesis work. A driving curiosity for this thesis work was founded by a 2013 experiment by Todd Humphreys, professor and researched at University of Texas at Austin, where he and his team successfully spoofed a yacht's navigation system [1]. A quote from Humphreys where he said "The ship actually turned and we could all feel it, but the chart display and the crew saw only a straight line" really sparked a deep curiosity for GPS. This curiosity was the driving motivator for this research project.

Although a GPS signal simulator is not a spoofing device it can be used to test anti-spoofing algorithms. The device presented herein attempts to set a foundation for future research by providing a robust GPS signal simulator with a modular architecture that can be configured to nearly all applications. The Radar and Microwaves Laboratory focus on passive radar research and the tools used for this research were available as resources. Given the hardware and software tools available in the laboratory, a signal simulator architecture design that utilizes those tools is put forth.

### **1.2** Thesis Organization

The organization of this thesis document attempts to build up on the information presented. Chapter 1 conducts a background discussion of the GPS signal characteristics, satellite orbital description, ground and air support systems, and augmented GPS. The methodology, chapter 2, details the procedures used in the construction of the GPS signal simulator. It starts by first describing the firmware, then the software design, followed by a GPS software decoder and signal acquisition procedures. Lastly, the results found during the construction of the GPS signal simulator are provided in chapter 4. A brief conclusion and discussion about possible future works closes out the document.

## Chapter 2

# **Background and Theory**

### 2.1 Global Positioning System

The NAVSTAR Global Positioning System, known as GPS, is a satellite navigation system owned and deployed by the United States of America. Its main purpose is to provide its users with navigation, positioning, and timing services. The need for such a system was proposed by several U.S. government organizations including the Department of Defense (DOD), the National Aeronautics and Space Administration (NASA), and the Department of Transportation (DOT) [2]. Although the current user base is both civilian and military, the initial objective for GPS was to provide the U.S. military with three-dimensional position determination. It was only after a civilian aircraft was shot down by the USSR Air Defense, killing 269 people, for deviating from its original route and flying into Soviet airspace [3] that President Ronald Reagan allowed GPS to be used in civilian applications.

The GPS program was launched in the early 1970s [4] with the first 11 GPS satellites launched between 1974 and 1985. These satellites were Block I satellites used to validate the concept and test various parts of the system. After the initial 11 Block I satellites the Air Force launched nine Block II satellites between 1989 and 1990, followed by 19 Block IIA satellites between 1990 and 1997, and 13 Block

IIR satellites launched between 1996 and 2004 [5]. Now, GPS is fully operational and meets all of the criteria put forth in the 1960s when it was first proposed. It currently is a dual-use system, providing the the Standard Position Service (SPS) for all civilian applications and Precise Position Service (PPS) for military use. The current GPS constellation consists of 31 active satellites, as of the publication of this thesis, in six orbital planes. Each plane has four to six satellites. The GPS constellation, shown in figure 2.1, is arranged in such a way that the user can expect between six to ten visible satellites at any point in time or position on earth.

Figure 2.1: GPS Constellation Map [6]

There are three segments that make up GPS: the space segment, control segment, and the user segment. The space segment was initially composed of a 24-satellite constellation arranged into six equally-spaced orbital planes [7]. The constellation expended three of the 24 slots and repositioned six satellites to make room for the addition of three new satellites. This occurred in June of 2011 and was known as the "Expandable 24" expansion. The current active GPS constellation consists of 31 total satellites under full operational capability (FOC) [8]. The 31 satellites include 27 used for GPS, three reserve satellites, and one test satellite. The expansion from 24-slot to 27-slot constellation improves coverage in parts of the world and ensures users are able to receive signals from at least four satellites from virtually any point on earth [9]. The control segment is charged with tracking all 31 satellites, monitoring their transmissions, and transfers data to the entire constellation. Ground facilities spread around the world make up the control segment. The location of these facilities, seen on figure 2.2, were strategically chosen to monitor the satellites with minimal downtime. The Master Control Station, located in Colorado, is charged with conducting the primary control segment functions. The Monitor Stations track the satellites as they pass overhead. The 11 ground antennas position around the world are used to communicate with the satellites.

The user segment is made up of the GPS receivers able to use the GPS signal to determine their position, velocity, and time. The use of GPS has spread among virtually every industry. From agriculture to sports, surveying to emergency service, GPS has become an integral part of our daily lives. As such, the development of the GPS signal generator presented in this research helps test such applications.

### **GPS Control Segment**

Updated May 2017

Figure 2.2: GPS Control Segment Map [7]

### 2.2 Orbital Description

GPS satellites operate in medium Earth orbit (MEO) at an altitude of about 20,000 km above the Earth's surface. Each satellite orbits around earth twice a day. MEO is characterize by an orbital altitude of 2000 km to 35,790 km, which is where most Global Navigation Satellite Systems (GNSS) operate. GPS satellites operate in six approximately-circular orbital planes and have an orbital period of 11 hours and 58 minutes. These orbital planes form an elliptical path focused around the center of the Earth. As part of the navigation message GPS provides the receivers with orbital description and satellite coordinates describing the position of the satellites within the orbital path. Accurate information about the satellites' position is needed for a GPS receiver to determine its position on Earth.

The forces acting on a satellite are the Earth's gravitational field, other bodies in space like the Sun, the Moon and solar radiation pressure [10]. The major force is Earth's gravitational field and it can be described using Newton's laws where the force acting on the satellite is described in equation 2.1. Force F is the product of the acceleration of the satellite a and its mass m. Then, the force is found by

$$F = ma = -G\frac{mM}{r^3}r\tag{2.1}$$

using the radial r, gravitational constant G, and Earth's mass M. The minus sign defines the attractive nature of the gravitational force [2]. Solving for the satellite's acceleration by taking the second derivative of the position solves to equation 2.2, where  $\mu = G \cdot M$

$$\frac{d^2r}{dt^2} = -\frac{\mu}{r^3}r\tag{2.2}$$

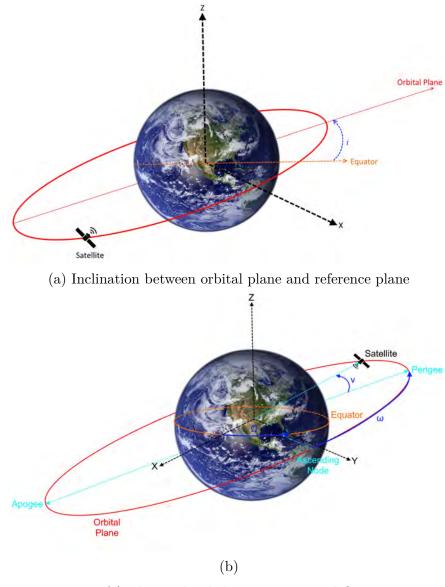

This equation is known as two-body or Keplerian motion equation where the only force acting on the satellite is the Earth [2] and describes the acceleration of the satellites with respect to Earth. A satellite, an object in motion in threedimensional space, has a position vector and a velocity vector each with x, y, and z component which dictates the use of six parameters to describe its trajectory. These parameters are known as Keplerian elements defined as semi-major axis, a, eccentricity, e, inclination, i, right ascension of the ascending node,  $\Omega$ , argument of perigee,  $\omega$ , and true anomaly, v. Figures 2.3a and 2.3b show four of the six orbital elements in reference to the orbital plane and the reference plane. The two orbital elements not shown in the figures due to graphical constraints are e and a.

The shape and size of the orbit are described by e and a. The e element is a number between 0 and 1 that describes the amount the orbit deviates from a perfect circle where e = 0 is a perfect circle. The a element is the mean between the apogee, a point on the orbital path furthest from the Earth's center, and the perigee, a point on the orbital path closest to the Earth's center. Equation 2.3 shows how erelates to the a and the semi-minor axis b. The orbital period  $T_p$ , which is time that it takes the satellite to complete one orbit around the Earth, of the satellite is calculated by equation 2.4. The orbital period has a direct relationship to the orbital altitude where the orbital altitude is the difference between the Earth's radius and the a.

$$e = \sqrt{1 - \frac{b^2}{a^2}} \tag{2.3}$$

$$T_p = 2\pi \sqrt{\frac{a^3}{\mu}} \tag{2.4}$$

(c) Three orbital elements,  $\omega$ , v, and  $\Omega$

Figure 2.3: Keplerian orbital elements

The orientation of the orbital plane is described by i,  $\Omega$ , and  $\omega$ . The position of the satellite is defined by v. The GPS receiver needs each of the six orbital planes for all of the satellites in the constellation. This information together with timing and angle corrections are contained in the ephemeris data encoded in the downlink message. A full list of the ephemeris data as defined by the GPS documentation is listed in table 2.1. Ephemeris data contain Keplerian elements containing periodic terms that correct gravitational perturbations.

- $t_{0_e}$  Reference time of ephemeris

- $\sqrt{a}$  Square root of the semi-major axis

- e Eccentricity

- $i_0$  Inclination angle a reference time

- $\Omega_0$  Longitude of the ascending node

- $\omega$  Argument of perigee

- $M_0$  Mean anomaly

- $\Omega$  Rate of change of longitude of the ascending node

- $\Delta n$  Mean motion correction

- $C_{u_c}$  Amplitude of cosine correction to argument of latitude

- $C_{u_s}$  Amplitude of sine correction to argument of latitude

- $C_{r_c}$  Amplitude of cosine correction to orbital radius

- $C_{r_s}$  Amplitude of sine correction to orbital radius

- $C_{i_c}$  Amplitude of cosine correction to inclination of angle

- $C_{i_s}$  Amplitude of sine correction to inclination of angle

Table 2.1: Ephemeris data definitions

### 2.3 Almanac and Ephemeris

The GPS almanac contains low-resolution ephemeris data about every satellite in the GPS constellations. Each satellite transmits almanac data for all satellites but transmits only its own ephemeris data. The almanac data includes satellite states (e.g., health), coarse ephemeris, an ionospheric model, and timing correction information. Both the almanac data and ephemeris data are contained within the GPS message signal which will be furthered discussed later in this chapter. The difference between ephemeris and almanac is one of detail: whereas ephemeris data is a detailed description of the satellite's orbital and timing characteristics while almanac data is a general description. Ephemeris data are typically valid for 4 hours from the time of transmission while the almanac data can be valid for several weeks if no significant changes occur in the constellation [11]. It is important to acknowledge the separation between the validity of both ephemeris and almanac data and the transmission of that data by the satellites. Due to the characteristics of the message signal (further discussed in this section), each satellite transmits ephemeris data every 30 seconds, but requires 12.5 minutes to transmit the complete almanac. This means that a GPS receiver can receive updated ephemeris data every 30 seconds but it would take roughly 12.5 minutes to attain all of the almanac data.

The control segment generates a new almanac once a day. The new almanac is transmitted to each satellite during its next communication with the control segment. The United States Coast Guard (USCG) logs almanacs in a public database [11]. The almanac data is saved in two formats called YUMA and SEM. Although both YUMA and SEM contain the same almanac data, the major difference is how the data are formatted. A YUMA almanac file separates the data in different lines, SEM clumps data together in the same line but different column. This formatting difference can be seen in figure 2.4, which shows a line-by-line snippet of the first satellite in the almanac.

| ID:<br>Health:<br>Eccentricity:<br>Time of Applicability(s):<br>Drbital Inclination(rad):<br>Rate of Right Ascen(r/s):<br>SQRT(A) (m 1/2):<br>Right Ascen at Week(rad):<br>Argument of Perigee(rad):<br>Mean Anom(rad):<br>Af0(s):<br>Af1(s/s):<br>week: | 0.9682738402<br>-0.7988904198E-008<br>5153.634277<br>0.3013838569E+001 | 31 CURRENT.ALM<br>933 405504<br>1<br>63<br>0<br>6.87313079833984E-03<br>5.15363427734375E+03<br>7.16657638549805E-02<br>0<br>11 | 9.59334611892700E-01 | -2.54294718615711E-09<br>1.85069799423218E-01<br>0.0000000000000000000000000000000000 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|

Figure 2.4: Different Almanac Formatting of Satellite with PRN 1

For this project the YUMA almanac format was chosen for two reasons. First the YUMA almanac file is more "human readable," meaning that the description of each data provided is listed; the SEM does not define the data in the file itself. Second it was faster to parse each line individually instead of parsing lines and spaces, as would have required with the SEM almanac format. However an advantage of using the SEM is that the data provided is already in the units of *semi-circles* or *semi-circles per seconds* while the YUMA almanac file kept all of its data in *radians* or *radians per second*. Using YUMA almanac required a conversion to the NAVSTAR standard, *semi-circles* an arbitrary choice that had no effect on the overall simulator quality.

### 2.4 GPS Signal Characteristics

The GPS satellites transmit navigation signals on two carrier frequencies called L1 and L2, both transmitted in the Ultra High Frequency (UHF) band that spans from 500 MHz to 3 GHz [12] and in particular in the L-band (1-2 GHz). These frequencies are derived from a single nominal reference frequency,  $f_0$ , at 10.23 MHz. Calculations for L1 and L2 are:

$$f_{\rm L1} = 154 \times f_0 = 1575.42 \quad \text{MHz}$$

(2.5)

$$f_{\rm L2} = 120 \times f_0 = 1227.60 \quad \text{MHz}$$

(2.6)

The carrier frequencies,  $f_{L1}$  and  $f_{L2}$ , contain GPS navigation data and uses three unique spreading sequences. The navigation data contains the information used by the GPS receivers to calculate position. The spreading sequence is a modulation method that widens the signal's bandwidth deliberately spreading it in the frequency domain. This type of modulation is typically done to ensure a secure communication, to decrease interference by other signals, or to prevent detection. The three spreading sequence used by GPS are the coarse acquisition code (C/A), precision (P) code, and the Y-code. The Y-code and P code are encrypted and referred to as P(Y) code, its encryption can only be decrypted by users with valid decryption key. The C/A code is not encrypted and for that reason it is used in civil applications making it the most widely used GPS signal. The C/A code is also used for acquisition of the P(Y) code by users with access to the signal. The frequency  $f_{L1}$  is modulated by both C/A and P(Y) code because until 2000 Selective Availability, a GPS mode that denied full accuracy of GPS to SPS users, was still active and required the P code encoding to deny full access to the signal. Frequency  $f_{L2}$  is modulated only by the P(Y) code and used by the PPS users. Interplexing scheme combines the C/A, P(Y) and the message data on a common carrier while keeping the signal envelope the same [13]. The transmitted signal is composed of two orthogonal components and can be written as:

$$S_{L1} = A_{P(Y)} \cdot P(t) \cdot D(t) \cdot \cos(2\pi \cdot f_{L1} \cdot t) + A_{C/A} \cdot C(t) \cdot D(t) \cdot \sin(2\pi \cdot f_{L1} \cdot t) \quad (2.7)$$

where the signal transmitted by the L1 channel,  $S_{L1}$ , is the sum of two orthogonal signals where  $A_{P(Y)}$  is the amplitude of the P(Y) code;  $P(t) = \pm 1$ , P(t) is the P(Y) code sequence,  $A_{C/A}$  is the amplitude of the C/A code;  $C(t) = \pm 1$ , D(t) is the message data code;  $D(t) = \pm 1$ , and C(t) is the C/A code sequence. The minimum L1 signal power level measure at the receiver are -133 dBm for P(Y) code and -130 dBm for the C/A code [14]. Typically the GPS receiver expects a L1 signal power level about 16 dB below the noise.

User position accuracy is the measurement of a three-dimension position using GPS signal. The user position accuracy of these signals is based on the reference of the transmitted signal by the satellite, this reference is referred to as the signal-in-space (SIS). The performance standard for SPS states that for L1 C/A code, single-frequency position accuracy is  $\leq 7.8$  meters 95% of the time [15]. The performance standard for PPS states that that L2 P(Y), the dual-frequency (both  $f_{L1}$  and  $f_{L2}$  being used) position accuracy is  $\leq 5.9$  meters 95% of the time [16]. With the use of differential GPS (discussed further in section 2.5.1) accuracy can improve to  $\leq 3$  meters for SPS and  $\leq 2$  meters for PPS. User position accuracy

is heavily dependent on the quality of the receiver, atmospheric conditions, and blocking of the signal due to building, bridges, trees, and other objects.

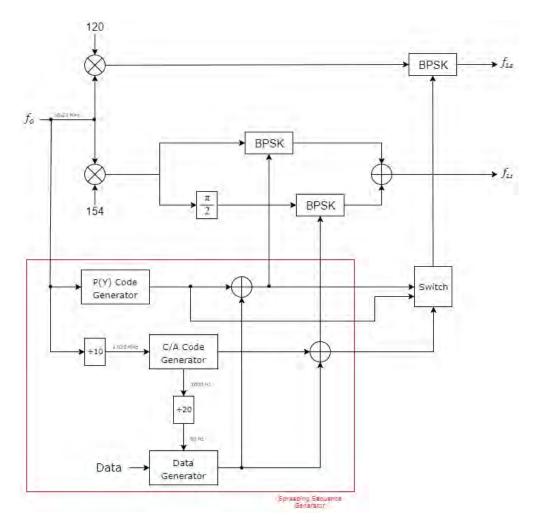

Each GPS satellite has the same signal structure and transmit both  $f_{L1}$  and  $f_{L2}$ . A simplified diagram of this signal structure is show in figure 2.5 where the derivation of both transmitted signals is clearly demonstrated. The diagram must be read form left to right (same as direction of data flow) to accurately depict the signal construction. It is important to note that the  $f_0$  is tuned to exactly 10.22999999543 MHz to adjust for relativistic effects but the observed frequency on by a GPS receiver is 10.23 MHz; therefore all depictions of the signal structure are from the receiver's perspective.

Current plans for GPS improvements are the addition of the L5 band, transmitted at 1176.45 MHz (or  $115 \times f_0$ ). This band is being developed for civilian safety-oflife providing a secure and robust signal to life critical applications. Compared to L1 C/A the new L5 band will enhance performance of the signal, have a higher transmitted power, and other upgrades. Lastly, GPS transmits at 1381.05 MHz (or  $135 \times f_0$ ) a signal used to detect nuclear detonations (NUDET) supported by the United States Nuclear Detonation Detection System (USNDS). This signal is referred to as the L3 band carrier signal and is part of the Detection System Payload.

Figure 2.5: SPS and PPS signal structure

The signal structure diagram references equations 2.5 and 2.6 where the  $f_0$  is multiplied by two constants, 120 for  $f_{L2}$  and 154 for  $f_{L1}$ . The bottom of diagram, encased by a red square, depicts the spreading sequence generators. Each of the two generator blocks, the C/A Code Generator and P(Y) Code Generator, produces a sequence of chips (bits that do not hold any information) which modulate the carriers. The C/A code generates a repeating sequence of 1023 chips at a rate of 1.023 MHz. The P(Y) code generates a sequence of about  $2.35 \times 10^6$  chips with a chip rate of 10.23 MHz. Each generated spreading sequence is multiplied to the data sequence of bits and modulated on to the L1 and L2 carriers using Binary Phase Shift Keying (BPSK) modulation. The C/A code is modulated only onto the L1 carrier frequency while the P(Y) code is modulated on both L1 and L2 carrier frequencies. The GPS control segment selects the spreading sequence modulated on to the L2 carrier. This is usually the P(Y) code but for unpublished reasons the control segment still has the option to switch between them, hence the switch block on the diagram.

#### 2.4.1 Binary Phase Shift Keying

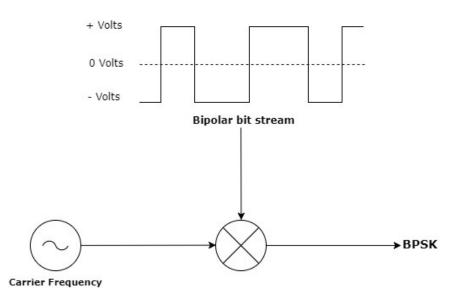

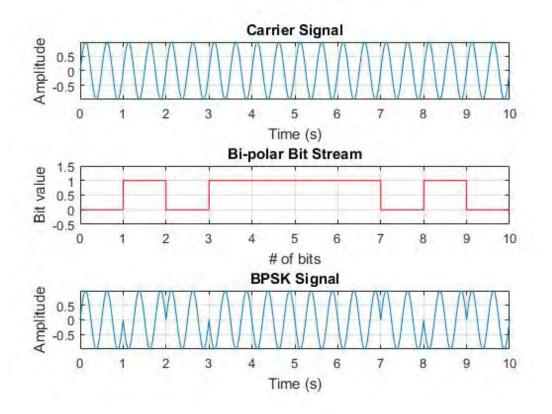

Using a sinusoidal signal as the carrier frequency and modulating it with a bipolar stream of bits will reverse the polarity of the sinusoidal signal, this is illustrated in figure 2.6.

Figure 2.6: Generation of BPSK on a sinusoidal carrier frequency

BPSK uses two phases separated by 180° which means that the carrier is either transmitted in its original form or with a phase shift. The change in phase occurs at the time of the bit change. The top graph in figure 2.7 shows a sinusoidal carrier signal at 2 Hz. This carrier signal is modulated by the square wave signal in the middle graph. The modulated signal is the BPSK signal shown in the bottom graph.

Figure 2.7: BPSK modulation

Observe the symmetrical shape of the BPSK signal in figure 2.7. This symmetry is caused by making the bit rate of the bipolar bit stream signal a sub-multiple of the carrier frequency. In GPS, this bipolar bit stream is the navigation data transmitted by the satellite. This navigation data is transmitted at a rate of 50 bits-per-second (bps) and modulated onto both the L1 and L2 carrier.

#### 2.4.1.1 Direct Sequence Spread Spectrum

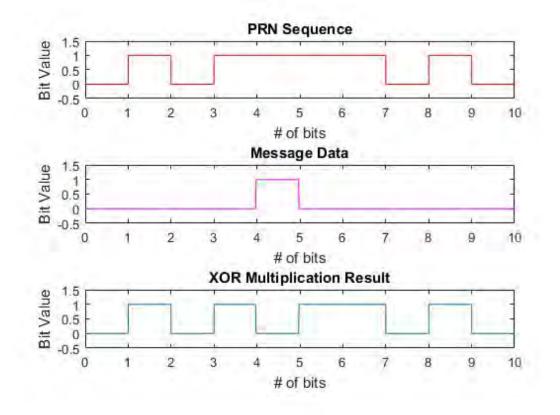

Direct Sequence Spread Spectrum (DSSS) extends BPSK by including a third signal called pseudo random noise (PRN) spreading code. PRN spreading code signal is similar to the data bit stream signal: it also contains a stream of -1 and 1 values, but at a significant higher chip rate. In GPS, the data bit stream is the navigational data and has a bit rate of 50 bps, while the PRN bit stream is the C/A code at a chip rate of 1.023 MHz (20460 times more than the navigational data bit rate). The PRN sequence is periodic, finite, and is completely known to the receiver.

The modulation of the carrier is done by taking the output of an exclusive-or, defined as XOR, multiplication of the PRN sequence and the navigation data, this is shown in figure 2.8. Only when the value of one of the two signals is high will the output of the XOR multiplication be high, this input/output relationship, called a truth table, is shown in table 2.2.

| Input |   | Output |  |

|-------|---|--------|--|

| 0     | 0 | 0      |  |

| 0     | 1 | 1      |  |

| 1     | 0 | 1      |  |

| 1     | 1 | 0      |  |

Table 2.2: Truth table of the XOR

Figure 2.8: XOR multiplication of two signals

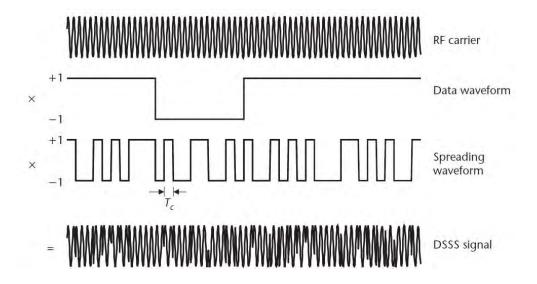

An illustration of how a DSSS modulation is applied can be seen in figure 2.9. The primary reason to use DSSS in GPS is to enable all of the satellites in the constellation to transmit on the same frequency. It is important to design proper PRN sequences so that cochannel interference can be reduced as small as possible [17]. The GPS C/A code uses the Gold code, a liner shift register sequence [18], with 1023 chip sequence.

Figure 2.9: DSSS modulation [2]

## 2.4.2 C/A Code

The C/A code is the spreading sequence used in the L1 channel and consists of a binary sequence of 1 and 0 states. This binary sequence is called a PRN code, which indicates that the code may appear random while being generated by a deterministic process. It has a chip rate of 1.023 MHz generated using a 1023 length Gold code. Equation 2.8 shows that the C/A code sequence repeats every 1 ms. The PRN code allows the access to the carrier signal, by despreding a specific PRN sequence the user can then extract the data from the carrier signal.

$$C/A_{chiprate} = \frac{1023}{1.023 \times 10^6 \,\mathrm{Hz}} = 1 \,\mathrm{ms}$$

(2.8)

Each satellite in the GPS constellation is assigned a satellite vehicle (SV) number and a PRN number. These numbers are not the same, but are unique to the constellation: whereas the SV number identifies the satellite, the PRN number identifies the PRN signal. When a receiver is acquiring a satellite signal, a locally generated C/A code is cross-correlated with the acquired signal which in turn removes nearly all of the other signals from other satellites form the acquired signal. This only works when the locally generated C/A code has the correct code phase. Therefore, multiple SVs can transmit under the same frequency but with different PRN codes and a receiver can receive the signal from multiple SVs and be able to separate them.

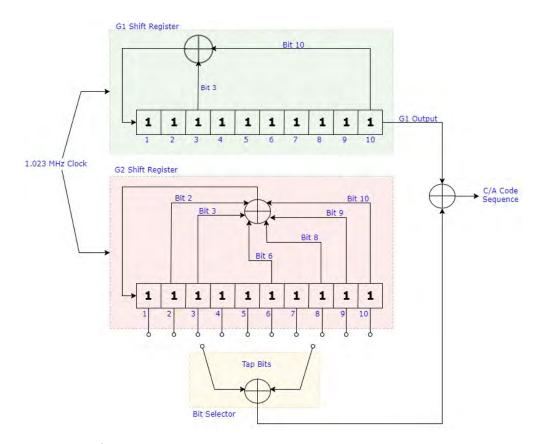

The generation of a C/A code is published in [19] with the intent to be replicated in civilian GPS receivers. GPS only works when all segments are coherent, meaning that the user segment must be properly develop in accordance with the published specifications in order to work with the space segment. Figure 2.10 shows the design schema of the C/A code generator where two shift registers and a bit selector are color coded to represent the important sections of the generator.

Figure 2.10: C/A code generator design schema.  $G_1$  register in green,  $G_2$  register in red, and the *Bit Selector* in yellow

The green section in the C/A code generator diagram shows the  $G_1$  shift register. It is a 10-bit shift register with an input clock of 1.023 MHz. The 10 bits on the register are shifted right at every rising edge of the input clock. Bit 10, the least significant bit (LSB), is shifted out of the register and all other 9 bits are shifted right. The value of bits 2 through 10 is described as  $G_1^*[n] = G_1[n-1]$ where n is the bit number. The left most bit depends on the XOR result of bits 3 and 10 and is described as  $G_1^*[1] = G_1[3] \oplus G_1[10]$ . The bit shifted out of the registered is used as one of the two input into the XOR that will result on the C/A code bit sequence. The red section in the diagram shows the  $G_2$  shift register. Much like the  $G_1$  register,  $G_2$  holds 10-bits and also shifts each bit to the right at the rising edge of the clock input. Both shift registers are synchronized to the same input clock, this means that the shifting happens at the same time in both registers. The value of the left most bit shifted into the register is described as  $G_2^*[1] = G_1[2] \oplus G_1[3] \oplus G_1[6] \oplus G_1[8] \oplus G_1[9] \oplus G_1[10]$ . The resulting value is 1 only when the compared bits have an odd number of bits equal to 1. The right most bit is shifted out of the register but not used. The feedback configuration of both registers can be represented using a polynomial equation, defined in equation 2.9 and 2.10, where the exponential value refer to the bit that is being fed back into the register. The output of register  $G_2$ , which is the bit used to be XOR compared with the output of the  $G_1$  register, is a combination of two bits. The two bits are chosen by the *Bit Selector*, identified as the yellow section in the diagram. The *Bit Selector* selects two of the 10 bits of the  $G_2$  register and the XOR comparison of those bits is then used to generate the C/A code sequence. Table 2.3 shows the bits that need to be selected by the *Bit Selector* to generate the desired C/A code sequence. Each bit pair is unique to a single SV except for PRN 34 and 37 which have the same bit pair and generating the same PRN sequence. PRN numbers 33 through 37 are never used for C/A code L1 signal, they have other uses.

$$f_{\rm G1}(x) = 1 + x^3 + x^{10} \tag{2.9}$$

$$f_{G2}(x) = 1 + x^2 + x^3 + x^6 + x^8 + x^9 + x^{10}$$

(2.10)

At the start of the sequence both registers are initialized to all ones and neither of the shift registers will ever be a sequence of all zero bits.

| PRN Number | Tap Bits      | First 10 Chips (Octal) |

|------------|---------------|------------------------|

| 1          | $2 \oplus 6$  | 1440                   |

| 2          | $3\oplus 7$   | 1620                   |

| 3          | $4 \oplus 8$  | 1710                   |

| 4          | $5\oplus9$    | 1744                   |

| 5          | $1 \oplus 9$  | 1133                   |

| 6          | $2 \oplus 6$  | 1455                   |

| 7          | $1 \oplus 8$  | 1131                   |

| 8          | $2 \oplus 9$  | 1454                   |

| 9          | $3 \oplus 10$ | 1626                   |

| 10         | $2\oplus 3$   | 1504                   |

| 11         | $3 \oplus 4$  | 1642                   |

| 12         | $5 \oplus 6$  | 1750                   |

| 13         | $6\oplus 7$   | 1764                   |

| 14         | $7\oplus 8$   | 1772                   |

| 15         | $8\oplus9$    | 1775                   |

| 16         | $9 \oplus 10$ | 1776                   |

| 17         | $1 \oplus 4$  | 1156                   |

| 18         | $2 \oplus 5$  | 1467                   |

| 19         | $3\oplus 6$   | 1633                   |

| 20         | $4 \oplus 7$  | 1615                   |

| 21         | $5\oplus 8$   | 1746                   |

| 22         | $6\oplus 9$   | 1763                   |

| 23         | $1\oplus 3$   | 1063                   |

| 24         | $4 \oplus 6$  | 1706                   |

| 25         | $5 \oplus 7$  | 1743                   |

| 26         | $6\oplus 8$   | 1761                   |

| 27         | $7\oplus9$    | 1770                   |

| 28         | $8 \oplus 10$ | 1774                   |

| 29         | $1 \oplus 6$  | 1127                   |

| 30         | $2 \oplus 7$  | 1453                   |

| 31         | $3\oplus 8$   | 1625                   |

| 32         | $4 \oplus 9$  | 1712                   |

| 33         | $5 \oplus 10$ | 1745                   |

| 34         | $4 \oplus 10$ | 1713                   |

| 35         | $1 \oplus 7$  | 1134                   |

| 36         | $2 \oplus 8$  | 1456                   |

| 37         | $4 \oplus 10$ | 1713                   |

|            |               |                        |

Table 2.3: C/A code bit assignment and first 10-chip sequence

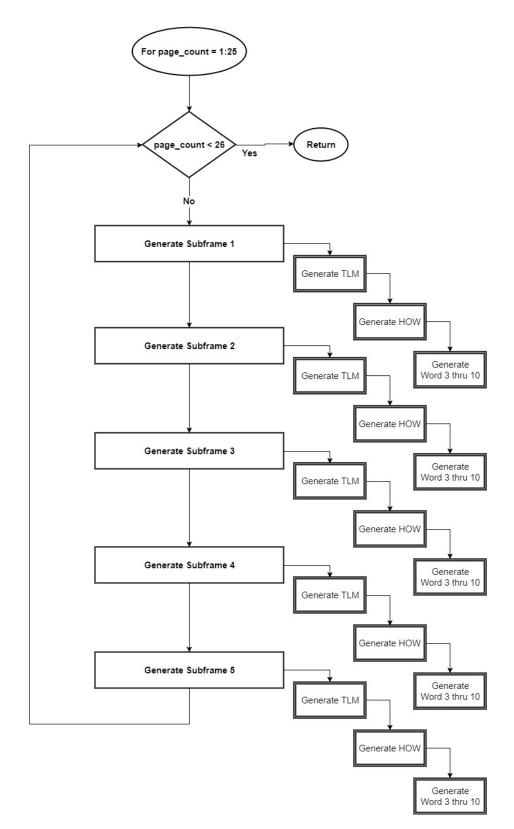

#### 2.4.3 Message Signal Format

Navstar specifications define how the message data are modulated onto the carrier signal [19]. It contains ephemeris data, health data, almanac data, and other useful data used by the receivers for navigation purpose. The navigation data is a stream of binary values, zeros and ones, that, together with the C/A code, is modulated onto the carrier signal. The navigation data rate is at 50 bits per second, meaning that every 2 ms a bit is generated. When modulated using DSSS modulation, the message signal is the slower sequence of binary bits, while the C/A code is the much faster sequence (refer back to section 2.4.1.1). Together these create the transmitted signal called SPS, or L1C (short for L1 C/A).

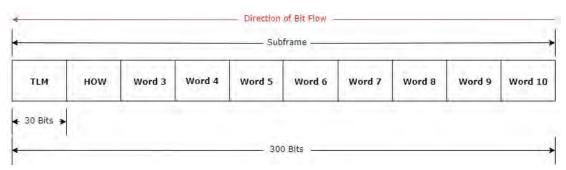

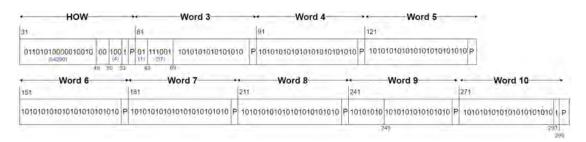

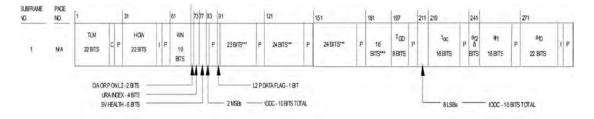

The navigation data are divided into pages, subframes, and words. A page is a collection of 5 subframes (a subframe is made up of 10 words) and a word is 300 bits. There are a total of 5 subframes, each containing specific data about the satellite or the constellation. Figure 2.11 shows a typical subframe structure as well as the size of each word, size of the subframe, and the direction the data flows out.

Figure 2.11: Subframe structure, size, and direction of data flow from SV

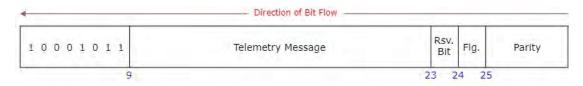

The data flows from left to right, meaning that the first bit transmitted is the left most bit of word 1. Word 1 is named TLM which is short for telemetry. The telemetry word is the first word of every subframe. It contains a preamble, an 8 bit known sequence used to identify the start of a new subframe. Figure 2.12 shows

the whole telemetry word starting with the 8-bit preamble, a telemetry message, one reserve bit, one status flag, and a 6 party bits. The telemetry message is a 14-bit-long message reserved to relay information about the PPS signal. The flag bit number 24 is an Integrity Status Flag (ISF). The last 6 bits are called the parity bits. Every word in every subframe reserves the last 6 bits for parity checking. These 6 bits are used by the receiver for error correction. The algorithm used for parity check is well-defined in [11] paragraph 20.3.5.2.

Figure 2.12: Telemetry word format

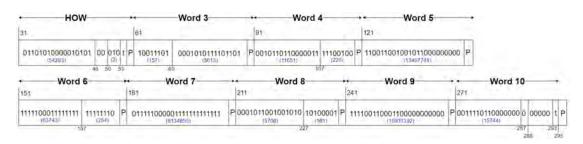

The HOW, short for handover word, is the second word of every subframe. The handover word starts with the time-of-the-week (TOW) count. The TOW (in the HOW word) is 17-bit truncated version of the 19-bit TOW count, and is an integer between 0 and 403,199, which equals to one full week. The full TOW count is the least significant bits of the Z-count, which is a time count that started in the night of January 5, 1980/ morning of January 6, 1980 [19]. The truncated TOW count maximum value is 100,799: once reached the count rolls over to zero and starts again. Figure 2.13 is the HOW word format including the TOW as the first 17 bits followed by two flags, bit 18 is the alert flag, and bit 19 is the anti-spoof flag. The 3-bit subframe ID represents the current subframe, with 000, 110, and 111 being invalid states. Bits 21 and 22 are used to solve for parity. In the HOW word, the last two parity bits, bits 29 and 30, must always be zeros. This is done by calculating the 'Solve Parity' bits such that, when calculating the parity, bits 29 and 30 are zero. Like the TOW word, the HOW data also flows right to left with the first bit of the TOW count being the first transmitted bit. The HOW word is always the second word in every subfame and always follows the TOW.

| * |                             | Direction     | of Bit      | Flow           |                 |        |   | _ |

|---|-----------------------------|---------------|-------------|----------------|-----------------|--------|---|---|

| - | Time-of-Week<br>(Truncated) | Alert<br>Flg. | A/S<br>Flg. | Subframe<br>ID | Solve<br>Parity | Parity | 0 | 0 |

| 1 | (Iruncated)                 | Fig.          | Flg.        | ID 20          | Parity          | 1.000  |   |   |

Figure 2.13: Handover word format

Words 3 through 10 vary depending on the subframe and page number. A short description of the eight words of data on each subframe is listed below. Refer to [19] for a full description of all the bits.

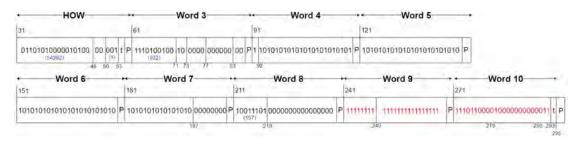

Subframe 1: Contains the GPS week number (relative to the epoch of midnight of January 6 1980), SV accuracy and health data (uses to determine if the SV is trustworthy), and clock correction data (to assist in computing the time the navigation message was transmitted from the SV).

Subframe 2 and 3: Contains the transmitting SV's ephemeris data which includes satellite orbits parameters, and correction terms used to calculate the transmitting SV's position.

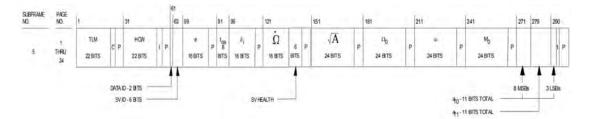

Subframe 4: This subframe is subcommuted 25 times, once in each page. Each page of subframe 4 contains the almanac and health data for SVs 25 through 32. Subframe 4 can have 4 different formats depending on the page number. Those different formats contain special messages, satellite configuration flags, Coordinated Universal Time (UTC), and ionospheric data, in addition to almanac data.

Subframe 5: This subframe is also subcommuted into 25 different pages. Unlike the previous subframe, this frame only uses two formats. These two formats contain almanac data for SVs 1 through 24, almanac reference time, week number, and health data.

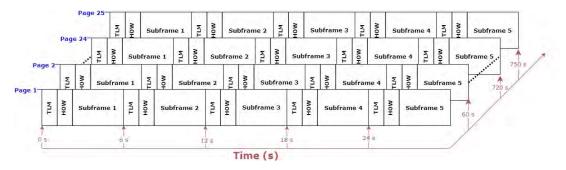

Figure 2.14 illustrates a time graph showing the transmission timing of the navigation data. At the start of the transmission, time = 0s, the first bit of the first word in subframe 1 is transmitted. The message data is transmitted at 50 bps, therefore the transmission of 30 bits takes 0.6 seconds, 300 bits takes 6 seconds, 5 subframes takes 30 seconds, and 25 pages takes 750 seconds. It takes 12.5 minutes (750 seconds) to receive a full GPS navigation message. Receivers with augmented GPS connect to a database to acquire almanac data, so do not require receiving the full navigation message before their position can be calculated.

Figure 2.14: Timing graph of the GPS message data

## 2.5 Augmentation Systems

GPS augmentation system helps improve the accuracy, integrity, or availability of GPS. Augmentation systems can be space-based, like geostationary satellite, or ground-based, like a network to help accuracy in cellular telephones. A different type of GPS augmentation can include sensors and compasses that provide navigation in areas where GPS is not available. Some vehicles integrate the use of inertial measuring units (IMU), which measure force, angular rate, and magnetic field, and blend results with GPS to enable navigation in places like tunnels, inside building. There are many augmentation systems worldwide, a few of which will be further discussed in this section.

### 2.5.1 Global Differential GPS

Sometimes called Nationwide Differential GPS (NDGPS), Differential GPS (DGPS) is a system that increases the accuracy and integrity of the GPS signal. These systems are ground-based and placed in areas where an increase in GPS accuracy is needed. The current DGPS Service is operated by the USCG and consists of one control center and forty-six broadcast sites [11]. These broadcast sites include weatherproof reference station antennas that broadcasting correction signals to improve position accuracy to better than 10 m to users who required better accuracy. The USCG transmits these correction signals in the long wave radio, frequencies between 285 kHz to 325 kHz, and typically near waterways and harbors. In 1993 the DOT calculated an estimated error growth in this system of 0.67 m per 100 km from the broadcasting site, further measurements in the Atlantic and Portugal suggested an error growth of just 0.22 m per 100 km [20]. The standard GPS accuracy of about 15 meters can be augmented to 10 m or better with DGPS [21].

#### 2.5.2 Wide Area Augmentation System

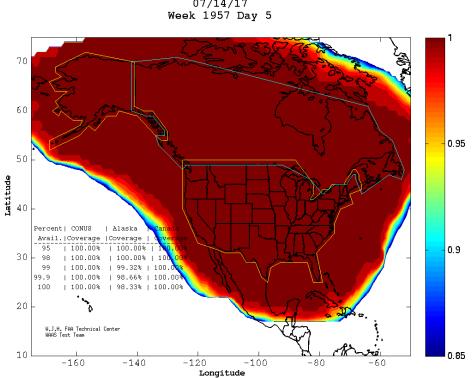

On August of 1994 the Federal Aviation Administration (FAA) and the DOT announced that a new GPS augmentation service for civil aviation was going to be deployed to improve navigation. The goal of this new service was to increase accuracy, integrity, and availability of GPS and enable aircraft to use it throughout all phases of flight. The Wide Area Augmentation System (WAAS) was commissioned in 2003 and is an extremely accurate system with requirements enabling a horizontal accuracy of 16 meters or less at least 95% and vertical accuracy of 4

meters or less at least 95% of the time. The FAA WAAS Test Team measured actual accuracy performed at horizontal accuracy of 0.7 m and vertical accuracy of 1.2 m [22]. Figure 2.15 shows WAAS coverage of localized performance with vertical guidance (LPV), which are the highest precision GPS with WASS enabled instrument approach procedures into airports, in the whole Continental U.S. and Canada. Compared to the GPS horizontal accuracy requirements of 36 meters and vertical accuracy requirements of 77 meters it is clear why civil aviation requires the use of WAAS for flight navigation, and landing sequences.

WAAS LPV Coverage Contours 07/14/17 Week 1957 Day 5

Figure 2.15: WASS LPV Coverage [23]

The current WAAS works by using 38 WAAS Reference Stations (WRS) spread around the US, Canada and Central America. These stations monitor GPS signals to determine position errors. The calculated position errors are sent to three WAAS Master Stations (WMS) via terrestrial communications. Augmentation messages are generated at each WMS, which contain information that removes errors from the GPS signal. WAAS sends the augmentation messages to three geostationary satellites which then relay the GPS-like message to GPS/WAAS receivers on Earth.

The implementation of WAAS in civil aviation has enabled landing approaches with visibility as low as 200 feet, improving airport access to places where instrument landing system (ILS) are not available. It has provided the direct navigation between two airports without the need of ground base navigation instruments like VHF omnidirectional range (VOR) signals or distance measuring equipment (DME).

# Chapter 3

# Methodology

# 3.1 GPS Signal Reproduction

The reproduction of the C/A L1 signal consisted of generating the PRN and Message data on firmware and software, respectively. The process used to reconstruct the signal is outlined in this section.

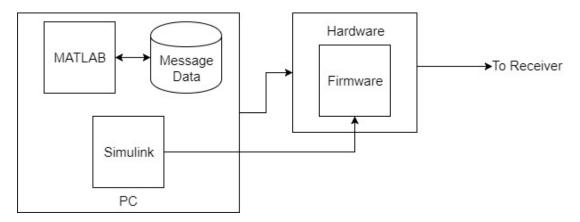

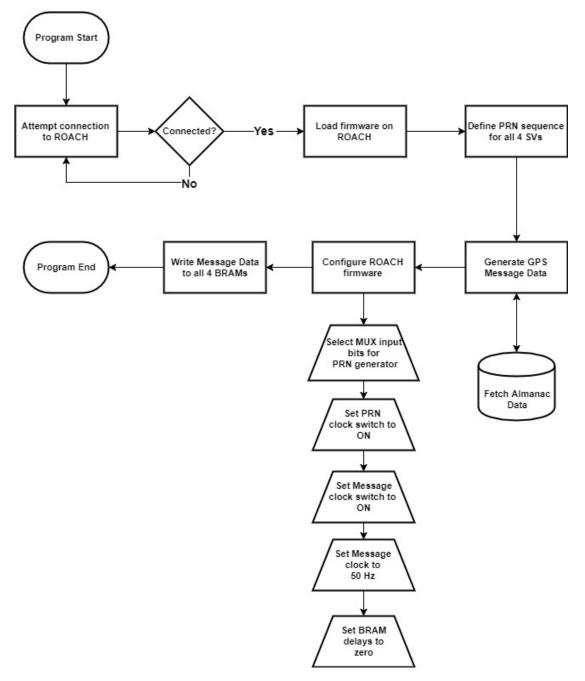

The GPS signal reproduction was done by a combination of firmware and software. The firmware programmed the hardware and generated the signal to be transmitted. The software constructed the data to be transmitted over the signal and controlled the firmware during execution. This relationship between software and hardware is described in the diagram on figure 3.1. The firmware was developed using Simulink, a block based programming tool, and the software was written in MATLAB, a popular programming tool used in signal processing.

Figure 3.1: Diagram showing connection between the software and the firmware

The reproduced signal was the L1 C/A GPS signal transmitted for civilian use all over the world. It consists of the PRN signal and message signal, which are both modulated onto the carrier frequency L1. This project simulated transmission of the GPS signal from four concurrent SVs, therefore the same signal structure was replicated four times with a few data points being changed to distinguish each SV.

The reproduced signal is a BPSK modulated signal with a spreading sequence. The signal is transmitted at 50.127 MHz and is modulated by a message data signal at 50 Hz and a spreading signal at 1.023 MHz. Each SV has a unique message signal and spreading sequence. The resulting transmitted signal is the sum of four independently modulated BPSK signals.

### 3.1.1 ROACH FPGA

The Collaboration for Astronomy Signal Processing and Electronics Research (CASPER) developed a serveral processing boards for radio astronomy. One of these boards is the Reconfigurable Open Architecture Computing Hardware (ROACH), a Field Programmable Gate Array (FPGA) based processing board that uses the CASPER and Xillinx, a FPGA manufacture, Simulink software blocks to provide signal analysis. The Radar and Microwaves Laboratory commissioned a set of ROACH processing boards to be used in various signal processing projects within the laboratory. The author of [24] provides a guide that details the setup of the ROACH and the software tools required for development of firmware. His application of the hardware and software environment was meant for real-time symbol recovery of digital television (DTV) signals for passive radar applications. Particular knowledge about the use of the software environment, the digital to analog converter (DACs), and access to the block random access memory (BRAM) was translated into this thesis project.

The ROACH runs on a Xilinx Virtex5 FPGA and an embedded AMCC PowerPC 440EPx processor [25]. The DAC used in this work is a Texas Instrument DAC5681 with 16 bit resolution and sample rate of 1 GS/s. The Simulink blocks used to develop the firmware for the thesis project was a combination between Xilinx and CASPER blocks. The Xilinx blocks performed logic targeting the FPGA and the CASPER blocks allowed control over the DAC and the BRAM.

#### 3.1.2 Firmware

The firmware is software written to internal memory and used to program the ROACH in order to generate the desired signal. The Simulink software tool was used to design the firmware. Blocks used within the Simulink model are blocks from the Xilinx and CASPER toolbox. These blocks, when connected together in a block flow, produce logic that is compiled to FPGA hardware descriptive language (HDL) and uploaded onto the ROACH's internal read-only memory.

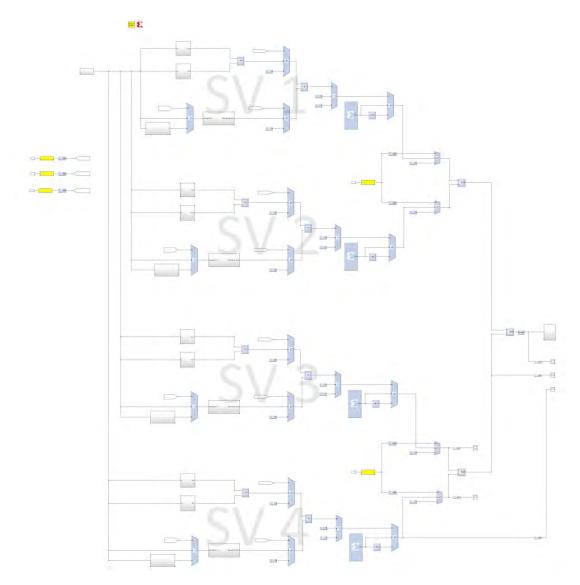

The firmware design requirement was to produce a sum of four GPS signals containing the PRN spreading sequence and the message data. The resulting firmware, shown in figure 3.2, meets the design requirements. In addition, it allows control over the number of signals being transmitted, configuration of the PRN sequence to be generated, independent message data storage for each signal, clock synchronization, and other testing modes allowing the live testing of the generated signal.

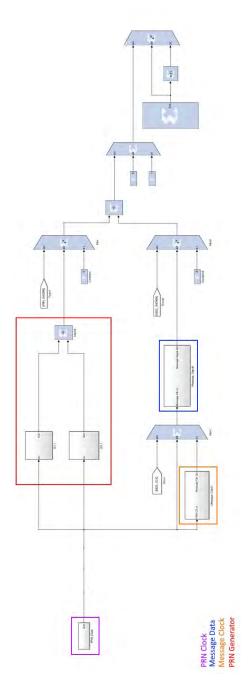

For simplicity, the firmware will be described in parts. Descriptions of each individual block follow the data flow from left to right. Because each SV signal has an exact signal architecture, the firmware will be initially described as a single signal model. The block logic that connects the four SV signals together and the composite four signal transmission will be described as the multisignal model. This breaks traditional Simulink terminology where each SV signal model would be referred to as subsystems. The declaration of subsystems has been reserved to each of the four signal components, PRN Clock, Message Clock, and Message Signal, and PRN Generator.

An important distinction to make is the difference between the system clock, and the model clock. The system clock is running at 200.508 MHz and is derived from the FPGA input clock at four times this rate. Therefore each clock tick, or clock count, happens at the rate of the system clock, 200.508 MHz. A bit transition, signal delay, or other logic happens at the rising edge of the input clock. Keeping each clock domain separate is of paramount importance in order to understand the firmware model and data flow. In addition, it is important to emphasize that all of the logic in the firmware is referenced by bit-by-bit logic that transitions at the rate of the input clock. Simulink blocks manipulate data at bit level precision, so conventional programming thinking does not apply.

Figure 3.2: Complete firmware flow diagram with markings identifying the signals of the four SVs

#### 3.1.2.1 Single Signal Model

The single signal model, shown in figure 3.3, generates a complete GPS signal from one SV. A complete GPS signal consists of the PRN signal, message signal, and the carrier frequency. Each of these subsystems are highlighted in the single signal model figure. The design called for the simulated GPS signal to be transmitted over a cable at the transmission frequency of 50.127 MHz. Future plans included an up-conversion of the simulated signal to the GPS L1 frequency, 1575.42 MHz. Critical relationship among the ADC rate  $f_{\rm adc}$ , which is 4 times the system clock  $f_{\rm sys}$ . The FPGA operates best for  $f_{\rm sys} \approx 200$  MHz. The 50.127 MHz clock is  $\frac{f_{\rm sys}}{4}$  (selected for ease of generating the subcarrier) and should have an integer number of code chips per cycle ( $\frac{50.127 \text{ MHz}}{1.023 \text{ MHz}} = 49$ ).

Figure 3.3: Block flow diagram of the single signal model highlighting the four subsystems

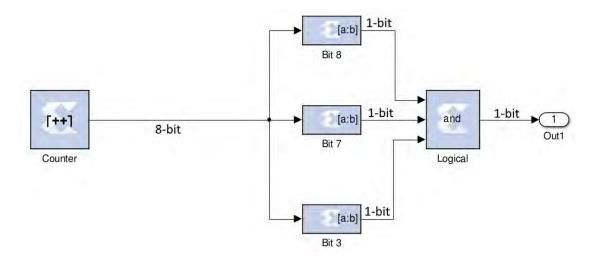

The PRN Clock, at 1.023 MHz, is the internal model clock. All logic is synchronized to this clock by setting the clock pulse of the logic block to the rising edge of the model clock. To generate a clock at this frequency, a clock divider logic was constructed. This logic used the system clock as an input to a counter. The counter counts to a number determined by equation 3.1. A high output is produced if and only if the counter has reach its maximum count, any other time the logic yields a low output.

$$Count_{int} = \frac{System_{clk}}{Desired_{clk}} \tag{3.1}$$

The PRN Clock subsystem used the clock divider logic to generate 1.023 MHz, the desired clock frequency, from 200.508 MHz, the system clock. Using equation 3.1, the counter maximum count is  $\frac{200.508MHz}{1.023MHz} = 196$ . The counter defines the maximum count as a 8-bit number because the least amount of digits needed to represent 196 is 8 digits. Using the binary equivalent of 196, '11000100', bits 8, 7 and 3 can be used to check if the maximum count has been reached. In other words the counter starts the count at '00000001' then progresses up to '1100100', the only time during the count that bits 8, 7 and 3 are all one is when it reaches the full count. The choice of starting the count at '00000001' is to reduce the number of bits that needs to be checked for maximum counter count. By connecting those three bits are high. This logic, used to generate the PRN Clock, is shown in figure 3.4. The three middle blocks labeled Bit 8, Bit 7, and Bit 3 are splice blocks used to splice specific bits from the incoming bit stream. These splice blocks are used throughout the firmware flow diagram.

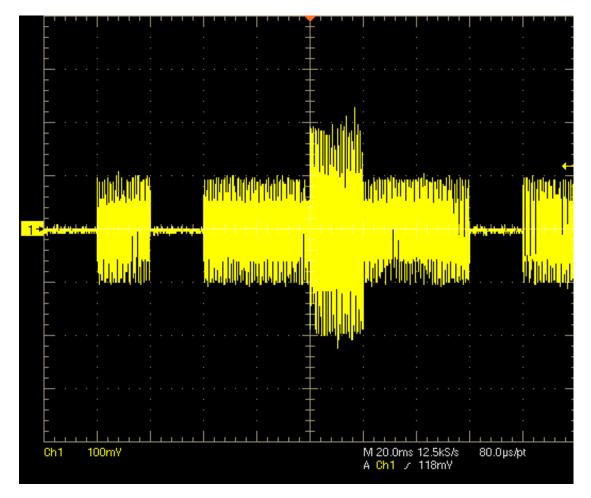

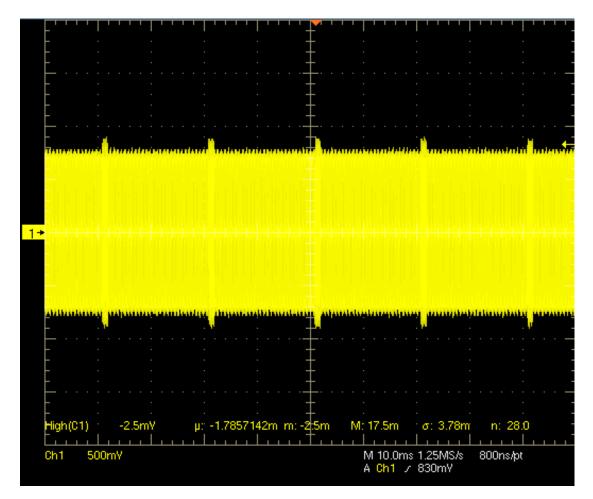

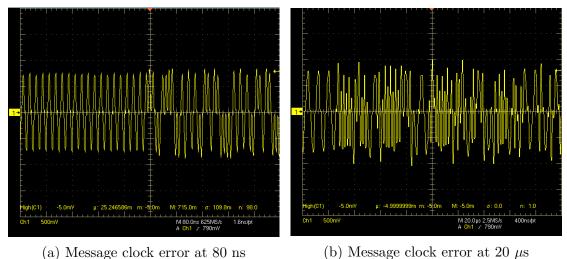

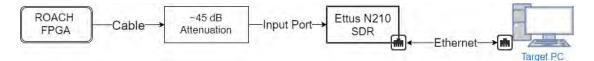

Figure 3.4: PRN Clock subsystem showing clock divider logic and bit stream size